ET-I2C TO 40 IO-DIN is I/O EXPANSION BOARD for 40-BIT MCU that is divided into 8-BIT 5-PORT and it is I2C BUS Interface. Specifications of this board are listed as follows;

## **SPECIFICATIONS**

- Use IC No.PCA9698DGG from NXP

- Use POWER SUPPLY 2.3V-5.5V

- Pin I/O can be set to be either 40-BIT INPUT and OUTPUT (8-BIT 5-PORT)

- Use I2C BUS Interface with the maximum Frequency at 1 MHz (Fast-Mode)

- Only use 3 Pin ADDRESS to setup and choose 64-Address of Board

- Can be fastened with Rail DIN 35mm

- PCB Size: 96.5 mm x 76.2 mm

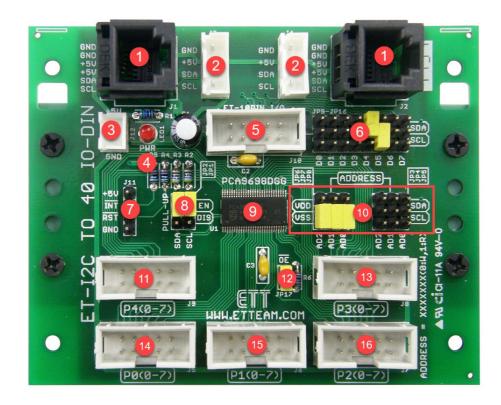

## **BOARD'S COMPONENTS**

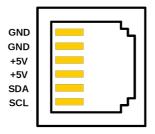

• No.1: It is Connector I2C RJ11 and Pins are arranged as shown below.

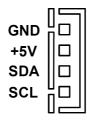

• No.2: It is Connector I2C WAFER and Pins are arranged as shown below.

• No.3: It is addition Connector POWER SUPPLY and Pins are arranged as shown below.

- No.4: It is LED to display state of POWER SUPPLY of board.

- No.5: It is Connector ET-10PIN I/O to connect with ETT Board that uses Connector 10PIN and Pins are arranged as shown below.

- No.6: It is JUMPER to choose Pin Signal from Connector ET-10PIN I/O to be either Pin SCL or Pin SDA.

Referred to the picture, Pin D4 is set to be Pin SDA and Pin D5 is set to be Pin SCL.

- No.7: It is PIN INTERRUPT and PIN RESET of IC No.PCA9698DGG.

- No.8: It is JUMPER to choose PULL-UP Resistor of Pin SCL and Pin SDA. If it is used, it is set to the position of EN; but, if it is unused, it is set to the position of DIS.

- No.9: It is IC No.PCA9698DGG.

- No.10: It is JUMPER to choose ADDRESS of Board. For more information, please look at the table below.

The example below chooses the value as ADDRESS 40h (AD2=VSS, AD1=VSS, AD0=VSS).

| PCA9698 address map |                 |                 |    |    |    |    |    |    |    |         |

|---------------------|-----------------|-----------------|----|----|----|----|----|----|----|---------|

| AD2                 | AD1             | AD0             | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Address |

| Vss                 | SCL             | Vss             | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 20h     |

| Vss                 | SCL             | $V_{DD}$        | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 22h     |

| Vss                 | SDA             | Vss             | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 24h     |

| V <sub>SS</sub>     | SDA             | $V_{DD}$        | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 26h     |

| V <sub>DD</sub>     | SCL             | Vss             | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 28h     |

| V <sub>DD</sub>     | SCL             | $V_{DD}$        | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 2Ah     |

| V <sub>DD</sub>     | SDA             | Vss             | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 2Ch     |

| V <sub>DD</sub>     | SDA             | $V_{DD}$        | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 2Eh     |

| V <sub>SS</sub>     | SCL             | SCL             | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 30h     |

| Vss                 | SCL             | SDA             | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 32h     |

| Vss                 | SDA             | SCL             | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 34h     |

| Vss                 | SDA             | SDA             | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 36h     |

| V <sub>DD</sub>     | SCL             | SCL             | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 38h     |

| V <sub>DD</sub>     | SCL             | SDA             | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 3Ah     |

| V <sub>DD</sub>     | SDA             | SCL             | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 3Ch     |

| V <sub>DD</sub>     | SDA             | SDA             | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 3Eh     |

| V <sub>SS</sub>     | V <sub>SS</sub> | V <sub>SS</sub> | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 40h     |

| V <sub>SS</sub>     | V <sub>SS</sub> | $V_{DD}$        | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 42h     |

| Vss                 | $V_{DD}$        | Vss             | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 44h     |

| Vss                 | $V_{DD}$        | $V_{DD}$        | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 46h     |

| V <sub>DD</sub>     | V <sub>SS</sub> | V <sub>SS</sub> | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 48h     |

| V <sub>DD</sub>     | $V_{SS}$        | $V_{DD}$        | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 4Ah     |

| V <sub>DD</sub>     | $V_{DD}$        | Vss             | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 4Ch     |

| V <sub>DD</sub>     | $V_{DD}$        | $V_{DD}$        | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 4Eh     |

| Vss                 | Vss             | SCL             | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 50h     |

| V <sub>SS</sub>     | V <sub>SS</sub> | SDA             | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 52h     |

| V <sub>SS</sub>     | $V_{DD}$        | SCL             | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 54h     |

| V <sub>SS</sub>     | $V_{DD}$        | SDA             | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 56h     |

| V <sub>DD</sub>     | V <sub>SS</sub> | SCL             | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 58h     |

| V <sub>DD</sub>     | V <sub>SS</sub> | SDA             | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 5Ah     |

| V <sub>DD</sub>     | V <sub>DD</sub> | SCL             | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 5Ch     |

| V <sub>DD</sub>     | $V_{DD}$        | SDA             | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 5Eh     |

|     | PC              | A9698 ad        | ddress i | mapco | ntinued |    |    |    |    |         |

|-----|-----------------|-----------------|----------|-------|---------|----|----|----|----|---------|

| AD2 | AD1             | AD0             | A6       | A5    | A4      | A3 | A2 | A1 | Α0 | Address |

| SCL | SCL             | Vss             | 1        | 0     | 1       | 0  | 0  | 0  | 0  | A0h     |

| SCL | SCL             | V <sub>DD</sub> | 1        | 0     | 1       | 0  | 0  | 0  | 1  | A2h     |

| SCL | SDA             | V <sub>SS</sub> | 1        | 0     | 1       | 0  | 0  | 1  | 0  | A4h     |

| SCL | SDA             | $V_{DD}$        | 1        | 0     | 1       | 0  | 0  | 1  | 1  | A6h     |

| SDA | SCL             | Vss             | 1        | 0     | 1       | 0  | 1  | 0  | 0  | A8h     |

| SDA | SCL             | V <sub>DD</sub> | 1        | 0     | 1       | 0  | 1  | 0  | 1  | AAh     |

| SDA | SDA             | Vss             | 1        | 0     | 1       | 0  | 1  | 1  | 0  | ACh     |

| SDA | SDA             | $V_{DD}$        | 1        | 0     | 1       | 0  | 1  | 1  | 1  | AEh     |

| SCL | SCL             | SCL             | 1        | 0     | 1       | 1  | 0  | 0  | 0  | B0h     |

| SCL | SCL             | SDA             | 1        | 0     | 1       | 1  | 0  | 0  | 1  | B2h     |

| SCL | SDA             | SCL             | 1        | 0     | 1       | 1  | 0  | 1  | 0  | B4h     |

| SCL | SDA             | SDA             | 1        | 0     | 1       | 1  | 0  | 1  | 1  | B6h     |

| SDA | SCL             | SCL             | 1        | 0     | 1       | 1  | 1  | 0  | 0  | B8h     |

| SDA | SCL             | SDA             | 1        | 0     | 1       | 1  | 1  | 0  | 1  | BAh     |

| SDA | SDA             | SCL             | 1        | 0     | 1       | 1  | 1  | 1  | 0  | BCh     |

| SDA | SDA             | SDA             | 1        | 0     | 1       | 1  | 1  | 1  | 1  | BEh     |

| SCL | V <sub>SS</sub> | Vss             | 1        | 1     | 0       | 0  | 0  | 0  | 0  | C0h     |

| SCL | V <sub>SS</sub> | V <sub>DD</sub> | 1        | 1     | 0       | 0  | 0  | 0  | 1  | C2h     |

| SCL | V <sub>DD</sub> | Vss             | 1        | 1     | 0       | 0  | 0  | 1  | 0  | C4h     |

| SCL | V <sub>DD</sub> | V <sub>DD</sub> | 1        | 1     | 0       | 0  | 0  | 1  | 1  | C6h     |

| SDA | Vss             | V <sub>SS</sub> | 1        | 1     | 0       | 0  | 1  | 0  | 0  | C8h     |

| SDA | Vss             | $V_{DD}$        | 1        | 1     | 0       | 0  | 1  | 0  | 1  | CAh     |

| SDA | V <sub>DD</sub> | Vss             | 1        | 1     | 0       | 0  | 1  | 1  | 0  | CCh     |

| SDA | V <sub>DD</sub> | V <sub>DD</sub> | 1        | 1     | 0       | 0  | 1  | 1  | 1  | CEh     |

| SCL | V <sub>SS</sub> | SCL             | 1        | 1     | 1       | 0  | 0  | 0  | 1  | E0h     |

| SCL | Vss             | SDA             | 1        | 1     | 1       | 0  | 0  | 1  | 0  | E2h     |

| SCL | V <sub>DD</sub> | SCL             | 1        | 1     | 1       | 0  | 0  | 1  | 1  | E4h     |

| SCL | V <sub>DD</sub> | SDA             | 1        | 1     | 1       | 0  | 1  | 0  | 0  | E6h     |

| SDA | V <sub>SS</sub> | SCL             | 1        | 1     | 1       | 0  | 1  | 0  | 1  | E8h     |

| SDA | V <sub>SS</sub> | SDA             | 1        | 1     | 1       | 0  | 1  | 1  | 0  | EAh     |

| SDA | V <sub>DD</sub> | SCL             | 1        | 1     | 1       | 0  | 1  | 1  | 1  | ECh     |

| SDA | V <sub>DD</sub> | SDA             | 1        | 1     | 1       | 0  | 0  | 0  | 1  | EEh     |

• No.11: It is Connector IDC10 for Pin IO4\_0 – IO4\_7 and Pins are arranged as shown below;

- No.12: It is JUMPER to enable/disable the operation of PCA9698DGG; normally, it is enabled.

- No.13: It is Connector IDC10 for Pin IO3\_0 IO3\_7 and Pins are arranged as shown below;

• No.14: It is Connector IDC10 for Pin IO0\_0 – IO0\_7 and Pins are arranged as shown below;

• No.15: It is Connector IDC10 for Pin IO1\_0 – IO1\_7 and Pins are arranged as shown below;

• No.16: It is Connector IDC10 for Pin IO2\_0 – IO2\_7 and Pins are arranged as shown below;

## EXAMPLE OF CONNECTING BOARD ET-I2C TO 40 IO-DIN WITH BOARD ARDUINO

This example illustrates how to connect with Boards ET-BASE AVR EASY328 as shown below;

It sets the value of Board ET-I2C TO 40 IO-DIN to be ADDRESS 40h (AD2=VSS, AD1=VSS, AD0=VSS) and connect signal between boards through Connector ET-10PIN I/O and Connector ANALOG [0..5] of Board ET-BASE AVR EASY328. In this case, Pin A4 is Pin SDA and Pin A5 is Pin SCL, so it has to set JUMPER on Board ET-I2C TO 40 IO-DIN; it has to set JUMPER D4 to be SDA and set JUMPER D5 to be SCL.

Open the Example Program PCA9698\_OUT in the Folder name Examples provided in CD-ROM. This Example Program illustrates how to send out the value to Port P0-P4 to upload program into Board. Next, it connects LED to test operation at Port P0-P4 (user can edit ADDRESS of Board as preferred, please look at the program below; in this case, this example sets the value as Address 0x40).

```

PCA9698_OUT | Arduino 1.8.4

File Edit Sketch Tools Help

PCA9698_OUT

1 /*

* Examples : Arduino Examples By....ETT CO.,LTD

* Program : PCA9698_OUT

* Software : Arduino 1.8.4

* Hardware : ET-BASE AVR EASY328 + ET-I2C TO 40 IO-DIN

* Function : Test output PCA9698

8

9 #include "Wire.h"

10 #define ADDR 0x40 >> 1

// Address for PCA9698 (AD2=VSS, AD1=VSS, AD0=VSS)

12 int out[8]={0x01,0x02,0x04,0x08,0x10,0x20,0x40,0x80};

13

14 void setup()

15 {

// Initial I2C Bus

16

Wire.begin();

17

18 // Set up ports 0-4

19

Wire.beginTransmission(ADDR);

20

Wire.write(0x00);

// PORT 0 for output

21

// PORT 1 for output

22

Wire.write(0x00):

23

Wire.write(0x00);

// PORT 2 for output

// PORT 3 for output

Wire.write(0x00);

25 Wire.write(0x00);

// PORT 4 for output

26

Wire.endTransmission();

27 }

```